# **Enhanced LIN Transceiver**

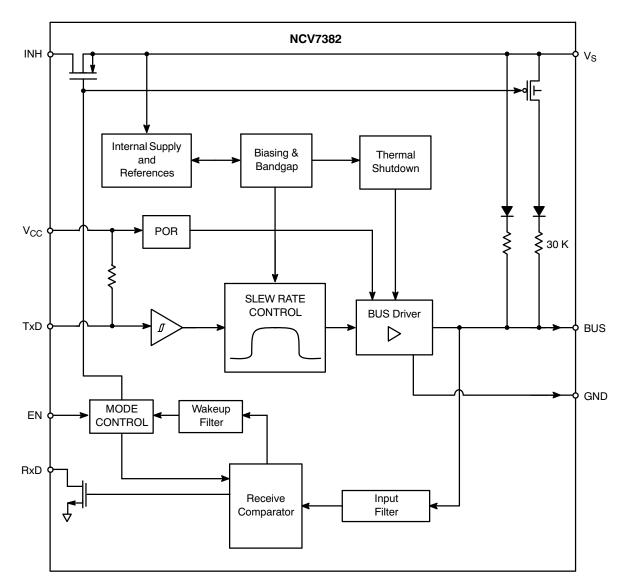

The NCV7382 is a physical layer device for a single wire data link capable of operating in applications where high data rate is not required and a lower data rate can achieve cost reductions in both the physical media components and in the microprocessor which uses the network. The NCV7382 is designed to work in systems developed for LIN 1.3 or LIN 2.0. The IC furthermore can be used in ISO9141 systems.

Because of the very low current consumption of the NCV7382 in the sleep mode it's suitable for ECU applications with low standby current requirements. This mode allows a shutdown of the whole application. The included wakeup function detects incoming dominant bus messages and enables the voltage regulator.

### Features

- Operating Voltage  $V_S = 7.0$  to 18 V

- $\bullet\,$  Very Low Standby Current Consumption of Typ. 6.5  $\mu A$  in Sleep Mode

- LIN-Bus Transceiver:

- Slew Rate Control for Good EMC Behavior

- Fully Integrated Receiver Filter

- BUS Input Voltage -27 V to 40 V

- Integrated Termination Resistor for LIN Slave Nodes (30 k $\Omega$ )

- Wakeup Via LIN Bus

- Baud Rate up to 20 kBaud

- Will Work in Systems Designed for Either LIN 1.3 or LIN 2.0

- Compatible to ISO9141 Functions

- High EMI Immunity

- Bus Terminals Protect Against Short-Circuits and Transients in the Automotive Environment

- High Impedance Bus Pin for Loss of Ground and Undervoltage Condition

- Thermal Overload Protection

- High Signal Symmetry for use in RC-Based Slave Nodes up to 2% Clock Tolerance when Compared to the Master Node

- ± 1000 V ESD Protection, Charged Device Model

- Control Output for Voltage Regulator with Low On-Resistance for Switchable Master Termination

- NCV Prefix for Automotive and Other Applications Requiring Site and Change Control

- AEC Qualified

- PPAP Capable

- Pb-Free Packages are Available

# **ON Semiconductor®**

http://onsemi.com

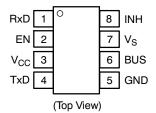

# **PIN CONNECTIONS**

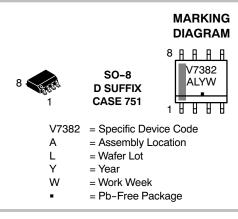

# **ORDERING INFORMATION**

| Device      | Package           | Shipping†        |

|-------------|-------------------|------------------|

| NCV7382D    | SO-8              | 95 Units/Rail    |

| NCV7382DG   | SO-8<br>(Pb-Free) | 95 Units/Rail    |

| NCV7382DR2  | SO-8              | 2500 Tape & Reel |

| NCV7382DR2G | SO-8<br>(Pb-Free) | 2500 Tape & Reel |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

# PACKAGE PIN DESCRIPTION

| Pin | Symbol          | Description                                                              |

|-----|-----------------|--------------------------------------------------------------------------|

| 1   | RXD             | Receive data from BUS to microprocessor, LOW in dominant state.          |

| 2   | EN              | Enables the normal operation mode when HIGH.                             |

| 3   | V <sub>CC</sub> | 5.0 V supply input.                                                      |

| 4   | TXD             | Transmit data from microprocessor to BUS, LOW in dominant state.         |

| 5   | GND             | Ground.                                                                  |

| 6   | BUS             | LIN bus pin, LOW in dominant state.                                      |

| 7   | V <sub>S</sub>  | Battery input voltage.                                                   |

| 8   | INH             | Control output for voltage regulator, termination pin for master pullup. |

# **Electrical Specification**

All voltages are referenced to ground (GND). Positive currents flow into the IC.

The maximum ratings (in accordance with IEC 134) given in the table below are limiting values that do not lead to a permanent damage of the device but exceeding any of these limits may do so. Long term exposure to limiting values may effect the reliability of the device.

### **OPERATING CONDITIONS**

| Characteristic                | Symbol          | Min | Max  | Unit |

|-------------------------------|-----------------|-----|------|------|

| V <sub>S</sub>                | V <sub>S</sub>  | 7.0 | 18   | V    |

| V <sub>CC</sub>               | V <sub>CC</sub> | 4.5 | 5.5  | V    |

| Operating Ambient Temperature | T <sub>A</sub>  | -40 | +125 | °C   |

#### MAXIMUM RATINGS

| Rating                                                                                          | Symbol               | Condition                                                                    | Min          | Max        | Unit |

|-------------------------------------------------------------------------------------------------|----------------------|------------------------------------------------------------------------------|--------------|------------|------|

| V <sub>S</sub>                                                                                  | VS                   | t < 1 min                                                                    |              | 30         | V    |

|                                                                                                 |                      | Load Dump, t < 500 ms                                                        | -0.3         | 40         |      |

| V <sub>CC</sub>                                                                                 | V <sub>CC</sub>      | -                                                                            | -0.3         | +7.0       | V    |

| Transient Supply Voltage                                                                        | V <sub>S.tr1</sub>   | ISO 7637/1 Pulse 1 (Note 1)                                                  | -150         | -          | V    |

| Transient Supply Voltage                                                                        | V <sub>Str2</sub>    | ISO 7637/1 Pulses 2 (Note 1)                                                 | -            | 100        | V    |

| Transient Supply Voltage                                                                        | V <sub>Str3</sub>    | ISO 7637/1 Pulses 3A, 3B                                                     | -150         | 150        | V    |

| BUS Voltage                                                                                     | V <sub>BUS</sub>     | t < 500 ms , Vs = 18 V                                                       | -27          | 40         | V    |

|                                                                                                 |                      | t < 500 ms ,Vs = 0 V                                                         | -40          | 40         |      |

| Transient Bus Voltage                                                                           | V <sub>BUStr1</sub>  | ISO 7637/1 Pulse 1 (Note 2)                                                  | -150         | -          | V    |

| Transient Bus Voltage                                                                           | V <sub>BUS.tr2</sub> | ISO 7637/1 Pulses 2 (Note 2)                                                 | -            | 100        | V    |

| Transient Bus Voltage                                                                           | V <sub>BUS.tr3</sub> | ISO 7637/1 Pulses 3A, 3B (Note 2)                                            | -150         | 150        | V    |

| DC Voltage on Pins TxD, RxD                                                                     | V <sub>DC</sub>      | -                                                                            | -0.3         | 7.0        | V    |

| ESD Capability, Charged Device Model                                                            | V <sub>ESDCDM</sub>  | (Note 3)                                                                     | -1.0         | 1.0        | kV   |

| ESD Capability of BUS, RxD, TxD, V <sub>CC</sub> , EN Pins ESD Capability of V <sub>S</sub> Pin | V <sub>ESDHBM</sub>  | Human Body Model, equivalent to discharge 100 pF with 1.5 $k\Omega$ (Note 3) | -2.0<br>-1.5 | 2.0<br>1.5 | kV   |

| Maximum Latchup Free Current at Any Pin                                                         | I <sub>LATCH</sub>   | -                                                                            | -500         | 500        | mA   |

| Maximum Power Dissipation                                                                       | P <sub>tot</sub>     | At $T_A = 125^{\circ}C$                                                      | _            | 197        | mW   |

| Thermal Impedance                                                                               | $\theta_{JA}$        | In Free Air                                                                  | -            | 152        | °C/W |

| Storage Temperature                                                                             | T <sub>stg</sub>     | -                                                                            | -55          | +150       | °C   |

| Junction Temperature                                                                            | TJ                   | -                                                                            | -40          | +150       | °C   |

# LEAD TEMPERATURE SOLDERING REFLOW

| Lead Free, 60 sec -150 sec above 217, 40 sec Max at Peak | T <sub>SLD</sub> | - | 265 Peak | °C |

|----------------------------------------------------------|------------------|---|----------|----|

| Leaded, 60 sec -150 sec above 183, 30 sec Max at Peak    | T <sub>SLD</sub> | - | 240 Peak | °C |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

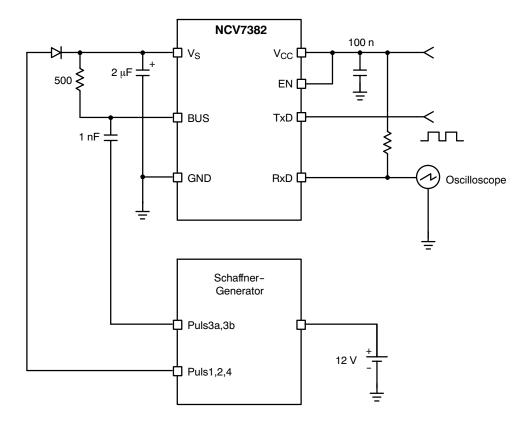

1. ISO 7637 test pulses are applied to  $V_S$  via a reverse polarity diode and > 2.0  $\mu$ F blocking capacitor. 2. ISO 7637 test pulses are applied to BUS via a coupling capacitance of 1.0 nF.

- 3. This device incorporates ESD protection and is tested by the following methods:

ESD HBM tested per AEC-Q100-002 (EIA/JESD22-A 114C) ESD CDM tested per EIA/JESD22-C 101C, Field Induced Model.

| Characteristic                       | Symbol                                      | Condition                                                                                                        | Min  | Тур | Max  | Unit |

|--------------------------------------|---------------------------------------------|------------------------------------------------------------------------------------------------------------------|------|-----|------|------|

| GENERAL                              | 1                                           | I                                                                                                                |      |     | 1    |      |

| V <sub>CC</sub> Undervoltage Lockout | V <sub>CC_UV</sub>                          | EN = H, TxD = L                                                                                                  | 2.75 | -   | 4.3  | V    |

| Supply Current, Dominant             | I <sub>Sd</sub>                             | $V_{\rm S}$ = 18 V, $V_{\rm CC}$ = 5.5 V, TxD = L                                                                | -    | 0.9 | 2.0  | mA   |

| Supply Current, Dominant             | I <sub>CCd</sub>                            | $V_{\rm S}$ = 18 V, $V_{\rm CC}$ = 5.5 V, TxD = L                                                                | -    | 0.6 | 2.0  | mA   |

| Supply Current, Recessive            | I <sub>Sr</sub>                             | $V_{\rm S}$ = 18 V, $V_{\rm CC}$ = 5.5 V TxD = H                                                                 | -    | 25  | 50   | μA   |

| Supply Current, Recessive            | I <sub>CCr</sub>                            | V <sub>S</sub> = 18 V, V <sub>CC</sub> = 5.5 V TxD = H                                                           | -    | 50  | 75   | μA   |

| Supply Current, Sleep Mode           |                                             | $V_S$ = 12 V, $V_{CC}$ and $TxD$ = 0 V, $T_A$ = 25°                                                              | -    | 6.5 | -    | μΑ   |

| Supply Current, Sleep Mode           | I <sub>Ssl</sub>                            | $V_{S}$ = 12 V, $V_{CC}$ and $TxD$ = 0 V                                                                         | -    | 6.5 | 14   | μA   |

| Thermal Shutdown                     | T <sub>sd</sub> (Note 4)                    | -                                                                                                                | 155  | -   | 180  | °C   |

| Thermal Recovery                     | T <sub>hys</sub> (Note 4)                   | -                                                                                                                | 126  | -   | 150  | °C   |

| BUS TRANSMIT                         | ·                                           |                                                                                                                  |      |     |      |      |

| Short Circuit Bus Current            | I <sub>BUS_LIM</sub><br>(Notes 5 and 6)     | $V_{BUS} = V_S$ , Driver On                                                                                      | -    | 120 | 200  | mA   |

| Pullup Current Bus                   | I <sub>BUS_PU</sub><br>(Notes 5 and 6)      | $V_{BUS}$ = 0, $V_{S}$ = 12 V, Driver Off                                                                        | -600 | -   | -200 | μΑ   |

| Pullup Current Bus                   | IBUS_PU_SLEEP                               | $V_{BUS} = 0, V_S = 12 V$ , Sleep Mode                                                                           | -100 | -75 | -    | μA   |

| Bus Reverse Current,<br>Recessive    | I <sub>BUS_PAS_rec</sub><br>(Notes 5 and 6) | V <sub>BUS</sub> > V <sub>S</sub> , 8.0 V < V <sub>BUS</sub> < 18 V<br>7.0 V < V <sub>S</sub> < 18 V, Driver Off | -    | -   | 20   | μΑ   |

| Bus Reverse Current Loss of Battery  | I <sub>BUS</sub><br>(Notes 5 and 6)         | $V_{S} = 0 V, 0 V < V_{BUS} < 18 V$                                                                              | -    | -   | 100  | μΑ   |

| Bus Current During Loss of Ground    | I <sub>BUS_NO_GND</sub><br>(Notes 5 and 6)  | V <sub>S</sub> = 12 V, 0 < V <sub>BUS</sub> < 18 V                                                               | -1.0 | -   | 1.0  | mA   |

| Transmitter Dominant Voltage         | V <sub>BUSdom_DRV_2</sub><br>(Note 5)       | $V_{S}$ = 7.0 V, Load = 500 $\Omega$                                                                             | -    | -   | 1.2  | V    |

| Transmitter Dominant Voltage         | V <sub>BUSdom_DRV_3</sub><br>(Note 5)       | $V_{S}$ = 18 V, Load = 500 $\Omega$                                                                              | -    | -   | 2.0  | V    |

# **BUS RECEIVE**

**Bus Input Capacitance**

| Receiver Dominant Voltage             | V <sub>BUSdom</sub><br>(Notes 5 and 6)   | -                                                                     | 0.4 *V <sub>S</sub>      | -                   | -                    | V |

|---------------------------------------|------------------------------------------|-----------------------------------------------------------------------|--------------------------|---------------------|----------------------|---|

| Receiver Recessive Voltage            | V <sub>BUSrec</sub><br>(Notes 5 and 6)   | -                                                                     | -                        | -                   | 0.6*V <sub>S</sub>   | V |

| Center Point of Receiver<br>Threshold | V <sub>BUS_CNT</sub><br>(Notes 4, 5 & 6) | V <sub>BUS_CNT</sub> = (V <sub>BUSdom</sub> + V <sub>BUSrec</sub> )/2 | 0.487<br>*V <sub>S</sub> | 0.5*V <sub>S</sub>  | 0.512*V <sub>S</sub> | V |

| Receiver Hysteresis                   | V <sub>HYS</sub><br>(Notes 4, 5 & 6)     | $V_{BUS\_CNTt} = (V_{BUSrec} - V_{BUSdom})$                           | -                        | 0.16*V <sub>S</sub> | -                    | V |

Pulse Response via 10 k $\Omega,$   $V_{PULSE}$  = 12 V,  $V_S$  = Open

\_

25

pF

35

No production test, guaranteed by design and qualification.

In accordance to LIN physical layer specification 1.3.

In accordance to LIN physical layer specification 2.0.

C<sub>BUS</sub> (Note 4)

### **ELECTRICAL CHARACTERISTICS** (V<sub>S</sub> = 7.0 to 18 V, V<sub>CC</sub> = 4.5 to 5.5 V and T<sub>A</sub> = -40 to 125°C unless otherwise noted.)

| Characteristic                           | Symbol                | Condition                                                         | Min                 | Тур | Мах                 | Unit |

|------------------------------------------|-----------------------|-------------------------------------------------------------------|---------------------|-----|---------------------|------|

| rxd, en                                  |                       |                                                                   |                     |     |                     |      |

| High Level Input Voltage V <sub>ih</sub> |                       | Rising Edge                                                       | -                   | -   | 0.7*V <sub>CC</sub> | V    |

| Low Level Input Voltage                  | V <sub>il</sub>       | Falling Edge                                                      | 0.3*V <sub>CC</sub> | -   | -                   | V    |

| TxD Pullup Resistor                      | R <sub>IH_TXD</sub>   | V <sub>TxD</sub> = 0 V                                            | 10                  | 15  | 25                  | kΩ   |

| EN Pulldown Resistor                     | R <sub>IL_EN</sub>    | V <sub>EN</sub> = 5.0 V                                           | 20                  | 30  | 50                  | kΩ   |

| RXD                                      | ·                     |                                                                   |                     |     |                     |      |

| Low Level Output Voltage                 | V <sub>ol_rxd</sub>   | $I_{RxD} = 2.0 \text{ mA}$                                        | -                   | -   | 0.9                 | V    |

| Leakage Current                          | V <sub>leak_rxd</sub> | V <sub>RxD</sub> = 5.5 V, Recessive                               | -10                 | -   | 10                  | μA   |

| NH                                       |                       |                                                                   |                     |     | ·                   |      |

| On Resistance R <sub>on_INH</sub>        |                       | Normal or Standby Mode,<br>$V_{INH} = V_S - 1.0 V$ , $V_S = 12 V$ | -                   | 20  | 50                  | Ω    |

| Leakage Current                          | I <sub>INH_Ik</sub>   | EN = L, V <sub>INH</sub> = 0 V                                    | -5.0                | -   | 5.0                 | μA   |

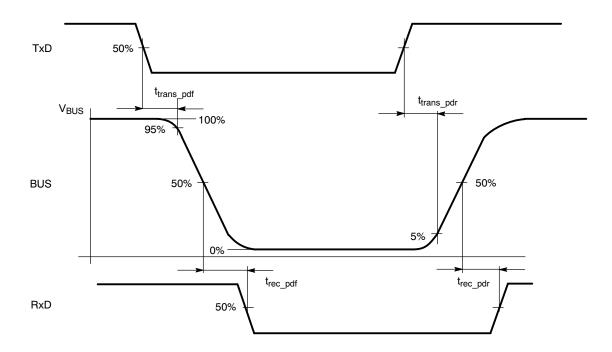

### **AC CHARACTERISTICS**

| Characteristic                                                          | Symbol                                           | Condition                                                                                                                            | Min        | Тур | Мах        | Unit           |

|-------------------------------------------------------------------------|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|------------|-----|------------|----------------|

| Propagation Delay Transmitter<br>(Notes 7 and 9)                        | t <sub>trans_pdf</sub><br>t <sub>trans_pdr</sub> | Bus Loads: 1.0 KΩ/1.0 nF,<br>660 Ω/6.8 nF, 500 Ω/10 nF                                                                               | -          | -   | 5.0        | μs             |

| Propagation Delay Transmitter Symmetry<br>(Notes 8 and 9)               | t <sub>trans_sym</sub>                           | Calculate t <sub>trans_pdf</sub> - t <sub>trans_pdr</sub>                                                                            | -2.0       | -   | 2.0        | μs             |

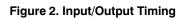

| Propagation Delay Receiver<br>(Notes 7, 9, 12, 13 and 14)               | t <sub>rec_pdf</sub><br>t <sub>rec_pdr</sub>     | C <sub>RxD</sub> = 20 pF                                                                                                             | -          | -   | 6.0        | μs             |

| Propagation Delay Receiver Symmetry<br>(Notes 9, 11 and 12)             | t <sub>rec_sym</sub>                             | Calculate t <sub>trans_pdf</sub> - t <sub>trans_pdr</sub>                                                                            | -2.0       | -   | 2.0        | μs             |

| Slew Rate Rising and Falling Edge,<br>High Battery (Notes 8, 11 and 12) | ltsr_нв                                          | Bus Loads: V <sub>S</sub> = 18 V,<br>1.0 KΩ/1.0 nF, 660 Ω/6.8 nF,<br>500 Ω/10 nF                                                     | 1.0        | 2.0 | 3.0        | V/µs           |

| Slew Rate Rising and Falling Edge,<br>Low Battery (Notes 8, 11 and 12)  | t <sub>SR_LB</sub>                               | Bus Loads: V <sub>S</sub> = 7.0 V,<br>1.0 KΩ/1.0 nF, 660 Ω/6.8 nF,<br>500 Ω/10 nF                                                    | 0.5        | 2.0 | 3.0        | V/µs           |

| Slope Symmetry, High Battery<br>(Notes 11 and 12)                       | t <sub>ssym_</sub> HB                            | Bus Loads: V <sub>S</sub> = 18 V,<br>1.0 kΩ/1.0 nF, 660 Ω/6.8 nF,<br>500 Ω/10 nF,<br>Calculate t <sub>sdom</sub> – t <sub>srec</sub> | -5.0       | -   | +5.0       | μs             |

| Bus Duty Cycle (Note 13)                                                | D1<br>D2                                         | $\begin{array}{l} Calculate \; t_{BUS\_rec(min)}/100 \; \mu s \\ Calculate \; t_{BUS\_rec(max)}/100 \; \mu s \end{array}$            | 0.396<br>- |     | _<br>0.581 | μs/μs<br>μs/μs |

| Receiver Debounce Time<br>(Notes 8, 11 and 14)                          | t <sub>rec_deb</sub>                             | BUS Rising and Falling Edge                                                                                                          | 1.5        | -   | 4.0        | μs             |

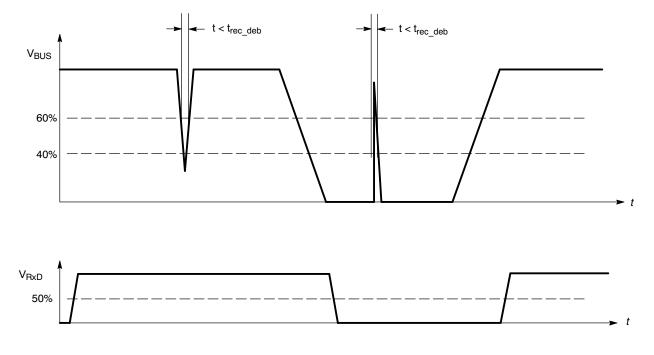

| Wakeup Filter Time                                                      | t <sub>wu</sub>                                  | Sleep Mode,<br>BUS Rising & Falling Edge                                                                                             | 30         | -   | 150        | μs             |

| EN - Debounce Time                                                      | t <sub>en_deb</sub>                              | Normal -> Sleep Mode Trans-<br>ition                                                                                                 | 10         | 20  | 40         | μs             |

7. Propagation delays are not relevant for LIN protocol transmission, value only information parameter.

8. No production test, guaranteed by design and qualification.

9. See Figure 2 - Input/Output Timing.

10. See Figure 8 - Slope Time Calculation.

11. See Figure 3 - Receiver Debouncing.

12. In accordance to LIN physical layer specification 1.3.

13. In accordance to LIN physical layer specification 2.0.

14. This parameter is tested by applying a square wave to the bus. The minimum slew rate for the bus rising and falling edges is 50 V/µs.

# TIMING DIAGRAMS

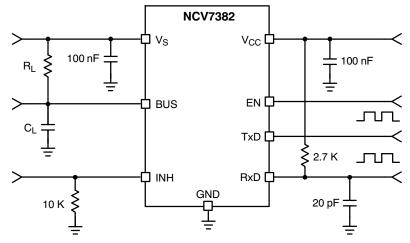

# TEST CIRCUITS FOR DYNAMIC AND STATIC CHARACTERISTICS

Figure 5. Test Circuit for Dynamic Characteristics

# **Functional Description**

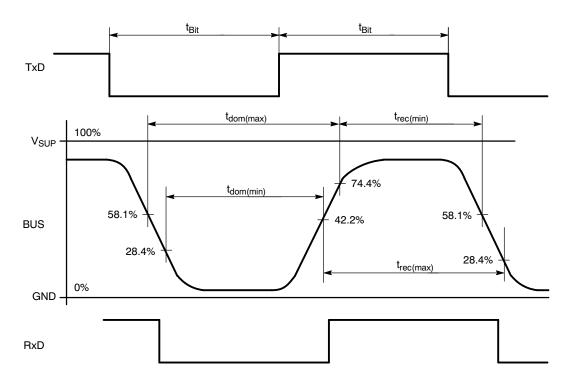

# Initialization

After *power on*, the chip automatically enters the  $V_{BAT}$ -standby mode. In this intermediate mode the INH output will become HIGH (V<sub>S</sub>) and therefore the ECU - voltage regulator will provide the V<sub>CC</sub>-supply. The transceiver will remain in the V<sub>BAT</sub> standby mode until the controller sets it to *normal operation* (EN = High). Bus communication is only possible in normal mode. The NCV7382 switches itself to the V<sub>BAT</sub>-standby mode if V<sub>CC</sub> is missing or below the undervoltage lockout threshold.

# **Operating Modes**

The EN pin is used to switch the NCV7382 into different operating modes.

# Normal Mode

All of the NCV7382 is active. Switching to normal mode can only be done with EN = high.

# Sleep Mode

Table 1. Mode Control

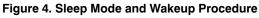

The *sleep mode* (EN = LOW) can only be reached from normal mode and permits a very low power consumption

because the transceiver and the external voltage regulator are disabled. If  $V_{CC}$  has been switched off, a wakeup request from the bus line (remote wakeup) will cause the NCV7382 to enter the  $V_{BAT}$ -standby mode ( $V_{CC}$  is present again) and sets the RxD output to low until the device enters the normal operation mode (active LOW interrupt at RxD). If the INH pin is not connected to the regulator or the inhibitable external regulator is not the one that provides the  $V_{CC}$  - supply, the normal mode is directly accessible by logic high on the EN pin. (Wakeup via mode change/local wakeup.)

In order to prevent an unintended wakeup caused by disturbances in the automotive environment, incoming dominant signals from the bus have to exceed the wakeup delay time.

# Thermal Shutdown Mode

If the junction temperature  $T_J$  is higher than 155°C, the NCV7382 could be switched into the thermal shutdown mode. Transmitter will be switched off.

If  $T_J$  falls below the thermal shutdown temperature (typ. 140°C), the NCV7382 will be switched to the previous state.

| EN | V <sub>CC</sub> | Comment                                                                            | INH      | RxD                                         |

|----|-----------------|------------------------------------------------------------------------------------|----------|---------------------------------------------|

| 0  | 0               | V <sub>BAT</sub> -standby, Power On                                                | Vs       | 0                                           |

| 0  | 1               | V <sub>BAT</sub> -standby, V <sub>CC</sub> On                                      | Vs       | Х                                           |

| 1  | 1               | Normal Mode                                                                        | Vs       | V <sub>CC</sub> = Recessive<br>0 = Dominant |

| 0  | 0               | Sleep Mode                                                                         | Floating | 0                                           |

| 0  | 1               | Sleep Mode<br>Regulator not disabled<br>Directly switch to normal mode with EN = 1 | Floating | V <sub>CC</sub>                             |

| 0  | 0/1             | Remote wakeup request                                                              | Vs       | 0 – Active low wakeup<br>interrupt          |

# LIN BUS Transceiver

The transceiver consists of a bus-driver (1.2 V @ 40 mA) with slew rate control, current limit, and a receiver with a high voltage comparator with filter circuitry.

# **BUS Input/Output**

The recessive BUS level is generated from the integrated 30 k pullup resistor in series with a diode. The diode prevents the reverse current on  $V_{BUS}$  when  $V_{BUS} > V_S$ .

No additional termination resistor is necessary to use the NCV7382 on LIN slave nodes. If this IC is used for LIN master nodes, it is necessary to terminate the bus with an external 1.0 k $\Omega$  resistor in series with a diode to V<sub>BAT</sub> or INH (See Section Short Circuit to Ground).

# TxD Input

During transmission the signal on TxD will be transferred to the BUS driver for generating a BUS signal. To minimize the electromagnetic emission of the bus line, the BUS driver has integrated slew rate control and wave shaping.

Transmitting will be interrupted in the following cases:

- Sleep Mode

- Thermal Shutdown

- V<sub>BAT</sub>-standby

The CMOS compatible input TxD directly controls the BUS level:

$TxD = low \rightarrow BUS = low (dominant level)$  $TxD = high \rightarrow BUS = high (recessive level)$

The TxD pin has an internal pullup resistor connected to  $V_{CC}$ . This secures that an open TxD pin generates a recessive BUS level.

#### **RxD Output**

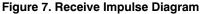

The signal on the BUS pin will be transferred continuously to the RxD pin. Short spikes on the bus signal are filtered with internal circuitry (Figure 3 and Figure 7).

The receive threshold values  $V_{BUS\_CNT\_max}$  and  $V_{BUS\_CNT\_min}$  are symmetrical to 0.5 \*  $V_S$  with a hysteresis of 0.16 \*  $V_S$  (typical). The LIN specific receive threshold is between 0.4 \*  $V_S$  and 0.6\* $V_S$ .

The received BUS signal will be output to the RxD pin:

BUS <  $V_{BUS}$ \_CNT - 0.5 \*  $V_{HYS}$  $\rightarrow$  RxD = low (BUS dominant)

BUS >  $V_{BUS\_CNT}$  + 0.5 \*  $V_{HYS}$  $\rightarrow$  RxD = high, floating (BUS recessive)

RxD is a buffered open drain output with a typical load of:

Resistance: 2.7 k $\Omega$ Capacitance: < 20 pF

#### **EN-Pin**

The NCV7382 is switched into sleep mode with a falling edge and into normal mode with a rising edge of the EN pin. It will remain in normal mode as long as EN = high (See Figure 4 – Sleep Mode and Wakeup Procedure for more details).

When the NCV7382 is switched to sleep mode, the voltage regulator on the INH pin is switched off.

The NCV7382 can be turned off with EN = low independent of the state of the bus-transceiver.

The EN input has an internal pulled down to guarantee a low level with EN floating.

# Data Rate

The NCV7382 is a *constant slew rate* transceiver. The bus driver operates with a fixed slew rate range of  $1.0 \text{ V/}\mu\text{s}$

$\leq \Delta V/\Delta T \leq 3.0 V/\mu s$ . This principle provides very good symmetry of the slope times between recessive to dominant and dominant to recessive slopes within the LIN bus load range (C<sub>BUS</sub>, R<sub>term</sub>).

The NCV7382 guarantees data rates up to 20 kbit within the complete bus load range under worst case conditions. The constant slew rate principle holds appropriate voltage levels and can operate within the LIN Protocol Specification for RC oscillator systems with a matching tolerance up to 2%.

#### **Operating Under Disturbance**

#### Loss of Battery

If  $V_S$  and  $V_{CC}$  are disconnected from the battery, the bus pin is in high impedance state. There is no impact to the bus traffic.

#### Loss of Ground

In case of an interrupted ground connection from  $V_S$  and  $V_{CC}$ , there is no influence to the bus line.

#### Short Circuit to Battery

The transmitter output current is limited to 200 mA (max) in case of short circuit to battery.

#### Short Circuit to Ground

Negative voltages on the BUS pin are limited primarily to current through the internal 30 k resistor and series diode from V<sub>S</sub> through a switched device controlled by EN.

Secondary contributions are attributed to the resistor and diode hardwired from  $V_S$  to BUS.

System designs can have an external resistor (1 k) in series with an external diode to the battery, but short circuit current from bus to ground can be reduced dramatically by using the INH pin as termination pin for the master pullup (See Figure 10 – Application Circuitry).

With this new setup, the controller can detect a short circuit of the bus to ground (RxD timeout) and the transceiver can be set into sleep mode. The INH pin will be floating in this case, and the external master pullup resistor will be disconnected from the bus line. Additionally, the internal slave termination resistor is switched off and only a high impedance termination is applied to the bus (typ. 75  $\mu$ A). This will reduce the failure current of the system by at least an order of magnitude, preventing a fast

### **Application Hints**

#### LIN System Parameter

Bus Loading Requirements

discharge of the car battery. If the failure is removed, the bus level will become recessive again and will wakeup the system even if no local wakeup is present or possible.

#### **Thermal Overload**

The NCV7382 is protected against thermal overloads. If the chip temperature exceeds the thermal shutdown threshold, the transmitter is switched off until thermal recovery. The receiver continues to work during thermal shutdown.

#### Undervoltage V<sub>CC</sub>

The  $V_{CC}$  undervoltage lockout feature disables the transmitter until it is above the undervoltage lockout threshold to prevent undesirable bus traffic.

| Parameter                                                           | Symbol                 | Min | Тур  | Max  | Unit             |

|---------------------------------------------------------------------|------------------------|-----|------|------|------------------|

| Operating Voltage Range                                             | V <sub>BAT</sub>       | 8.0 | -    | 18   | V                |

| Voltage Drop of Reverse Protection Diode                            | V <sub>Drop_rev</sub>  | 0.4 | 0.7  | 1.0  | V                |

| Voltage Drop at the Serial Diode in Pullup Path                     | V <sub>SerDiode</sub>  | 0.4 | 0.7  | 1.0  | V                |

| Battery Shift Voltage                                               | V <sub>Shift_BAT</sub> | 0   | -    | 0.1  | V <sub>BAT</sub> |

| Ground Shift Voltage                                                | V <sub>Shift_GND</sub> | 0   | -    | 0.1  | V <sub>BAT</sub> |

| Master Termination Resistor                                         | R <sub>master</sub>    | 900 | 1000 | 1100 | Ω                |

| Slave Termination Resistor                                          | R <sub>slave</sub>     | 20  | 30   | 60   | kΩ               |

| Number of System Nodes                                              | Ν                      | 2.0 | -    | 16   | -                |

| Total Length of Bus Line                                            | LEN <sub>BUS</sub>     | -   | -    | 40   | m                |

| Line Capacitance                                                    | C <sub>LINE</sub>      | -   | 100  | 150  | pF/m             |

| Capacitance of Master Node                                          | C <sub>Master</sub>    | -   | 220  | -    | pF               |

| Capacitance of Slave Node                                           | C <sub>Slave</sub>     | -   | 220  | 250  | pF               |

| Total Capacitance of the Bus including Slave and Master Capacitance | C <sub>BUS</sub>       | 1.0 | 4.0  | 10   | nF               |

| Network Total Resistance                                            | R <sub>Network</sub>   | 537 | -    | 863  | Ω                |

| Time Constant of Overall System                                     | τ                      | 1.0 | -    | 5.0  | μs               |

#### **Recommendations for System Design**

The goal of the LIN physical layer standard is to have a universal definition of the LIN system for plug and play solutions in LIN networks up to 20 kbd bus speeds.

In case of small and medium LIN networks, it's recommended to adjust the total network capacitance to at least 4.0 nF for good EMC and EMI behavior. This can be done by setting only the master node capacitance. The slave node capacitance should have a unit load of typically 220 pF for good EMC/EMI behavior.

In large networks with long bus lines and the maximum number of nodes, some system parameters can exceed the defined limits and of the LIN system designer must intervene.

The whole capacitance of a slave node is not only the unit load capacitor itself. Additionally, there is the capacitance of wires and connectors, and the internal capacitance of the LIN transmitter. This internal capacitance is strongly dependent on the technology of the IC manufacturer and should be in the range of 30 pF to 150 pF. If the bus lines have a total length of nearly 40 m, the total bus capacitance can exceed the LIN system limit of 10 nF.

A second parameter of concern is the integrated slave termination resistor tolerance. If most of the slave nodes have a slave termination resistance at the allowed maximum of 60 k $\Omega$ , the total network resistance is more than 700  $\Omega$ . Even if the total network capacitance is below or equal to the maximum specified value of 10 nF, the network time constant is higher than 7.0  $\mu$ s.

This problem can be solved only by adjusting the master termination resistor to the required maximum network time constant of  $5.0 \ \mu s$  (max).

MIN/MAX SLOPE TIME CALCULATION (In accordance to the LIN System Parameter Table)

NOTE: The setting of the network time constant is necessary in large networks (primarily resistance) and also in small networks (primarily capacitance). requires the deviation of the slave node clock to the master node clock after synchronization must not differ by more than  $\pm 2\%$ .

The NCV7382 meets the requirements for implementation in RC-based slave nodes. The LIN Protocol Specification

Figure 8. Slope Time and Slew Rate Calculation (In accordance to LIN physical layer specification 1.3)

The slew rate of the bus voltage is measured between 40% and 60% of the output voltage swing (linear region). The output voltage swing is the difference between dominant and recessive bus voltage.

$dV/dt = 0.2 * V_{swing}/(t_{40\%}-t_{60\%})$

The slope time is the extension of the slew rate tangent until the upper and lower voltage swing limits:

$t_{slope} = 5 * (t_{40\%} - t_{60\%})$

The slope time of the recessive to dominant edge is directly determined by the slew rate control of the transmitter:

### $t_{slope} = V_{swing}/dV/dt$

The dominant to recessive edge is influenced from the network time constant and the slew rate control, because it's a passive edge. In case of low battery voltages and high bus loads the rising edge is only determined by the network. If the rising edge slew rate exceeds the value of the dominant one, the slew rate control determines the rising edge.

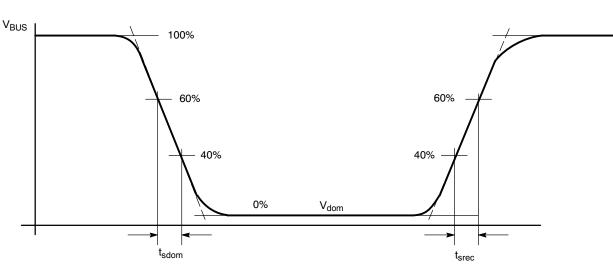

Figure 9. Duty Cycle Measurement and Calculation in Accordance to LIN Physical Layer Specification 2.0

### **Duty Cycle Calculation**

With the timing parameters shown in Figure 9 two duty cycles, based on  $t_{rec(min)}$  and  $t_{rec(max)}$  can be calculated as follows:

$$D1^* = t_{rec(min)}/(2 x t_{Bit})$$

$$D2^* = t_{rec(max)}/(2 x t_{Bit})$$

For proper operation at 20 kBit/s (bit time is 50  $\mu$ s) the LIN driver has to fulfill the duty cycles specified in the AC characteristics for supply voltages of 7...18 V and the three defined standard loads.

Due to this simple definition there is no need to measure slew rates, slope times, transmitter delays and dominant voltage levels as specified in the LIN physical layer specification 1.3.

The devices within the D1/D2 duty cycle range also operates in applications with reduced bus speed of 10.4 kBit/s or below.

In order to minimize EME, the slew rates of the transmitter can be reduced (by up to  $\approx 2$  times). Such devices have to fulfill the duty cycle definition D3/D4 in the LIN physical layer specification 2.0. Devices within this duty cycle range *cannot* operate in higher frequency 20 kBit/s applications.

\*D1 and D2 are defined in the LIN protocol specification 2.0.

Figure 10. Application Circuitry

# **ESD/EMC Remarks**

# **General Remarks**

Electronic semiconductor products are sensitive to Electro Static Discharge (ESD). Always observe Electro Static Discharge control procedures whenever handling semiconductor products.

# ESD Test

The NCV7382 is tested according to MIL883D (human body model).

# EMC

The test on EMC impacts is done according to ISO 7637-1 for power supply pins and ISO 7637-3 for data and signal pins.

# POWER SUPPLY PIN VS

| Test Pulse | Condition                                                                         | Duration              |  |

|------------|-----------------------------------------------------------------------------------|-----------------------|--|

| 1          | $t_1 = 5.0 \text{ s/U}_{\text{S}} = -100 \text{ V/t}_{\text{D}} = 2.0 \text{ ms}$ | 5000 Pulses           |  |

| 2          | $t_1 = 0.5 \text{ s/U}_{\text{S}} = 100 \text{ V/t}_{\text{D}} = 0.05 \text{ ms}$ | 5000 Pulses           |  |

| 3a/b       | U <sub>S</sub> = -150 V/U <sub>S</sub> = 100 V<br>Burst 100 ns/10 ms/90 ms Break  | 1 h                   |  |

| 5          | $R_i = 0.5 \Omega, t_D = 400 ms$<br>$t_r = 0.1 ms/U_P + U_S = 40 V$               | 10 Pulses Every 1 Min |  |

# DATA AND SIGNAL PINS EN, BUS

| Test Pulse | Condition                                                                         | Duration    |

|------------|-----------------------------------------------------------------------------------|-------------|

| 1          | $t_1 = 5.0 \text{ s/U}_{\text{S}} = -100 \text{ V/t}_{\text{D}} = 2.0 \text{ ms}$ | 1000 Pulses |

| 2          | $t_1 = 0.5 \text{ s/U}_{\text{S}} = 100 \text{ V/t}_{\text{D}} = 0.05 \text{ ms}$ | 1000 Pulses |

| 3a/b       | U <sub>S</sub> = -150 V/U <sub>S</sub> = 100 V<br>Burst 100 ns/10 ms/90 ms Break  | 1000 Burst  |

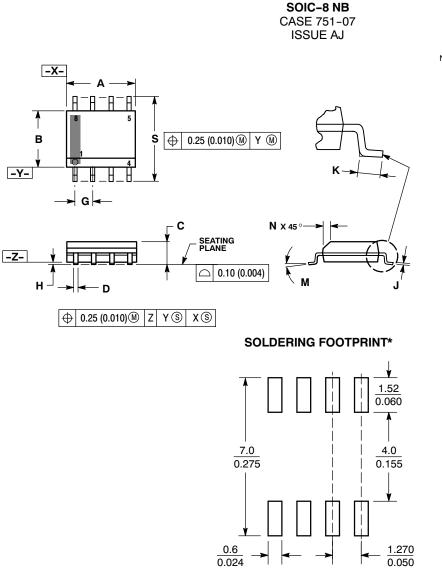

#### PACKAGE DIMENSIONS

NOTES:

- 1. DIMENSIONING AND TOLERANCING PER

- ANSI Y14.5M, 1982. 2. CONTROLLING DIMENSION: MILLIMETER.

- DIMENSION A AND B DO NOT INCLUDE MOLD PROTRUSION.

- MOLD PROTRUSION.

MAXIMUM MOLD PROTRUSION 0.15 (0.006) PER SIDE.

- DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127 (0.005) TOTAL IN EXCESS OF THE D DIMENSION AT MAXIMUM MATERIAL CONDITION.

- 6. 751-01 THRU 751-06 ARE OBSOLETE. NEW STANDARD IS 751-07.

|     | MILLIMETERS |      | INCHES    |       |

|-----|-------------|------|-----------|-------|

| DIM | MIN         | MAX  | MIN       | MAX   |

| Α   | 4.80        | 5.00 | 0.189     | 0.197 |

| В   | 3.80        | 4.00 | 0.150     | 0.157 |

| С   | 1.35        | 1.75 | 0.053     | 0.069 |

| D   | 0.33        | 0.51 | 0.013     | 0.020 |

| G   | 1.27 BSC    |      | 0.050 BSC |       |

| н   | 0.10        | 0.25 | 0.004     | 0.010 |

| J   | 0.19        | 0.25 | 0.007     | 0.010 |

| κ   | 0.40        | 1.27 | 0.016     | 0.050 |

| М   | 0 °         | 8 °  | 0 °       | 8 °   |

| Ν   | 0.25        | 0.50 | 0.010     | 0.020 |

| S   | 5.80        | 6.20 | 0.228     | 0 244 |

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

$\left(\frac{mm}{inches}\right)$

SCALE 6:1

ON Semiconductor and I are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use event is such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support: Phone: 421 33 790 9910

Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81-3-5773-3850 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your loca Sales Representative