**Vishay Siliconix**

## N-Channel 30-V (D-S) MOSFET

| PRODUCT SUMMARY     |                                  |                                 |                       |  |  |  |

|---------------------|----------------------------------|---------------------------------|-----------------------|--|--|--|

| V <sub>DS</sub> (V) | <b>R<sub>DS(on)</sub> (</b> Ω)   | I <sub>D</sub> (A) <sup>a</sup> | Q <sub>g</sub> (Typ.) |  |  |  |

| 30                  | 0.0035 at V <sub>GS</sub> = 10 V | 40 <sup>g</sup>                 | 21.5 nC               |  |  |  |

| 30                  | 0.0051 at $V_{GS}$ = 4.5 V       | 40 <sup>g</sup>                 | 21.5110               |  |  |  |

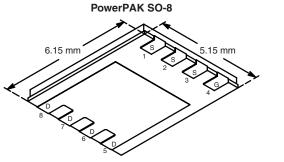

Bottom View

Ordering Information: SiR466DP-T1-GE3 (Lead (Pb)-free and Halogen-free)

#### FEATURES

- Halogen-free

- TrenchFET<sup>®</sup> Power MOSFET

- 100 % R<sub>g</sub> Tested

- 100 % UIS Tested

#### **APPLICATIONS**

- DC/DC Converter

Low Side Switch

- Notebook PC

- Graphic Cards

- Server

D

| Parameter                                          | Symbol                            | Limit           | Unit                 |     |  |

|----------------------------------------------------|-----------------------------------|-----------------|----------------------|-----|--|

| Drain-Source Voltage                               |                                   | V <sub>DS</sub> | 30                   | V   |  |

| Gate-Source Voltage                                |                                   | V <sub>GS</sub> | ± 20                 |     |  |

|                                                    | T <sub>C</sub> = 25 °C            |                 | 40 <sup>g</sup>      |     |  |

| Continuous Drain Current (T <sub>1</sub> = 150 °C) | T <sub>C</sub> = 70 °C            | I               | 40 <sup>g</sup>      |     |  |

| Continuous Drain Current (1) = 150 C)              | T <sub>A</sub> = 25 °C            | I <sub>D</sub>  | 28 <sup>b, c</sup>   |     |  |

|                                                    | T <sub>A</sub> = 70 °C            |                 | 22.5 <sup>b, c</sup> | Α   |  |

| Pulsed Drain Current                               |                                   | I <sub>DM</sub> | 70                   |     |  |

| Continuous Source-Drain Diode Current              | T <sub>C</sub> = 25 °C            | la la           | 40 <sup>g</sup>      |     |  |

| Continuous Source-Drain Diode Current              | T <sub>A</sub> = 25 °C            | I <sub>S</sub>  | 4.5 <sup>b, c</sup>  |     |  |

| Single Pulse Avalanche Current                     | L = 0.1 mH                        | I <sub>AS</sub> | 30                   |     |  |

| Single Pulse Avalanche Energy                      | L = 0.1 mm                        | E <sub>AS</sub> | 45                   | mJ  |  |

|                                                    | T <sub>C</sub> = 25 °C            |                 | 54                   |     |  |

| Maximum Power Dissipation                          | T <sub>C</sub> = 70 °C            | P <sub>D</sub>  | 34.7                 | w   |  |

|                                                    | T <sub>A</sub> = 25 °C            | ' D             | 5.0 <sup>b, c</sup>  | ~~~ |  |

|                                                    | T <sub>A</sub> = 70 °C            |                 | 3.2 <sup>b, c</sup>  |     |  |

| Operating Junction and Storage Temperature Ra      | T <sub>J</sub> , T <sub>stg</sub> | - 55 to 150     | °C                   |     |  |

| Soldering Recommendations (Peak Temperature        |                                   | 260             |                      |     |  |

#### THERMAL RESISTANCE RATINGS

| Parameter                                   | Symbol       | Typical           | Maximum | Unit |      |  |

|---------------------------------------------|--------------|-------------------|---------|------|------|--|

| Maximum Junction-to-Ambient <sup>b, f</sup> | t ≤ 10 s     | R <sub>thJA</sub> | 20      | 25   | °C/W |  |

| Maximum Junction-to-Case (Drain)            | Steady State | R <sub>thJC</sub> | 1.8     | 2.3  | °C/W |  |

Notes:

a. Based on  $T_C = 25$  °C.

b. Surface Mounted on 1" x 1" FR4 board.

c. t = 10 s.

- d. See Solder Profile (http://www.vishay.com/ppg?73257). The PowerPAK SO-8 is a leadless package. The end of the lead terminal is exposed copper (not plated) as a result of the singulation process in manufacturing. A solder fillet at the exposed copper tip cannot be guaranteed and is not required to ensure adequate bottom side solder interconnection.

- e. Rework Conditions: manual soldering with a soldering iron is not recommended for leadless components.

f. Maximum under Steady State conditions is 65 °C/W.

g. Package Limited.

| Parameter                                     | Symbol                  | Test Conditions                                                                                  | Min. | Тур.     | Max.   | Unit   |  |

|-----------------------------------------------|-------------------------|--------------------------------------------------------------------------------------------------|------|----------|--------|--------|--|

| Static                                        |                         |                                                                                                  |      | <u> </u> |        |        |  |

| Drain-Source Breakdown Voltage                | V <sub>DS</sub>         | $V_{GS} = 0 V, I_{D} = 250 \mu A$                                                                | 30   |          |        | V      |  |

| V <sub>DS</sub> Temperature Coefficient       | $\Delta V_{DS}/T_{J}$   | L 050 A                                                                                          |      | 31       |        | mV/°C  |  |

| V <sub>GS(th)</sub> Temperature Coefficient   | $\Delta V_{GS(th)}/T_J$ | l <sub>D</sub> = 250 μA                                                                          |      | - 5.4    |        |        |  |

| Gate-Source Threshold Voltage                 | V <sub>GS(th)</sub>     | $V_{DS} = V_{GS}, I_D = 250 \ \mu A$                                                             | 1.2  |          | 2.4    | V      |  |

| Gate-Source Leakage                           | I <sub>GSS</sub>        | $V_{DS} = 0 V, V_{GS} = \pm 20 V$                                                                |      |          | ± 100  | nA     |  |

|                                               |                         | $V_{DS} = 30 \text{ V}, V_{GS} = 0 \text{ V}$                                                    |      |          | 1      | μA     |  |

| Zero Gate Voltage Drain Current               | IDSS                    | $V_{DS} = 30 \text{ V}, \text{ V}_{GS} = 0 \text{ V}, \text{ T}_{J} = 55 ^{\circ}\text{C}$       |      |          | 10     |        |  |

| On-State Drain Current <sup>a</sup>           | I <sub>D(on)</sub>      | $V_{DS} \ge 5 \text{ V}, V_{GS} = 10 \text{ V}$                                                  | 30   |          |        | Α      |  |

|                                               |                         | V <sub>GS</sub> = 10 V, I <sub>D</sub> = 15 A                                                    |      | 0.0029   | 0.0035 |        |  |

| Drain-Source On-State Resistance <sup>a</sup> | R <sub>DS(on)</sub>     | V <sub>GS</sub> = 4.5 V, I <sub>D</sub> = 10 A                                                   |      |          | 0.0051 | Ω<br>1 |  |

| Forward Transconductance <sup>a</sup>         | g <sub>fs</sub>         | V <sub>DS</sub> = 15 V, I <sub>D</sub> = 15 A                                                    |      | 65       |        | S      |  |

| Dynamic <sup>b</sup>                          |                         |                                                                                                  |      |          | I      |        |  |

| Input Capacitance                             | C <sub>iss</sub>        |                                                                                                  |      | 2730     |        |        |  |

| Output Capacitance                            | C <sub>oss</sub>        | V <sub>DS</sub> = 15 V, V <sub>GS</sub> = 0 V, f = 1 MHz                                         |      | 540      |        | pF     |  |

| Reverse Transfer Capacitance                  | C <sub>rss</sub>        |                                                                                                  |      | 205      |        |        |  |

|                                               | Qg                      | $V_{DS} = 15 \text{ V}, V_{GS} = 10 \text{ V}, I_{D} = 10 \text{ A}$                             |      | 42.5     | 65     | 1      |  |

| Total Gate Charge                             |                         |                                                                                                  |      | 21.5     | 33     | nC     |  |

| Gate-Source Charge                            | Q <sub>gs</sub>         | $V_{DS}$ = 15 V, $V_{GS}$ = 4.5 V, $I_{D}$ = 10 A                                                |      | 6.9      |        |        |  |

| Gate-Drain Charge                             | Q <sub>gd</sub>         |                                                                                                  |      | 7.1      |        |        |  |

| Gate Resistance                               | Rg                      | f = 1 MHz                                                                                        | 0.2  | 0.8      | 1.6    | Ω      |  |

| Turn-On Delay Time                            | t <sub>d(on)</sub>      |                                                                                                  |      | 12       | 24     |        |  |

| Rise Time                                     | t <sub>r</sub>          | $V_{DD}$ = 15 V, $R_L$ = 1.5 $\Omega$                                                            |      | 9        | 18     |        |  |

| Turn-Off Delay Time                           | t <sub>d(off)</sub>     | $I_D \cong$ 10 A, $V_{GEN}$ = 10 V, $R_g$ = 1 $\Omega$                                           |      | 29       | 50     |        |  |

| Fall Time                                     | t <sub>f</sub>          |                                                                                                  |      | 9        | 18     |        |  |

| Turn-On Delay Time                            | t <sub>d(on)</sub>      |                                                                                                  |      | 30       | 50     | ns     |  |

| Rise Time                                     | t <sub>r</sub>          | $V_{DD}$ = 15 V, $R_L$ = 1.5 $\Omega$                                                            |      | 19       | 35     | -      |  |

| Turn-Off Delay Time                           | t <sub>d(off)</sub>     | $\text{I}_\text{D} \cong$ 10 A, $\text{V}_\text{GEN}$ = 4.5 V, $\text{R}_\text{g}$ = 1 $\Omega$  |      | 35       | 60     |        |  |

| Fall Time                                     | t <sub>f</sub>          |                                                                                                  |      | 15       | 30     |        |  |

| Drain-Source Body Diode Characteris           | tics                    |                                                                                                  |      | •        |        | •      |  |

| Continuous Source-Drain Diode Current         | ۱ <sub>S</sub>          | T <sub>C</sub> = 25 °C                                                                           |      |          | 40     | ٨      |  |

| Pulse Diode Forward Current <sup>a</sup>      | I <sub>SM</sub>         |                                                                                                  |      |          | 70     | A      |  |

| Body Diode Voltage                            | V <sub>SD</sub>         | I <sub>S</sub> = 3 A                                                                             |      | 0.74     | 1.1    | V      |  |

| Body Diode Reverse Recovery Time              | t <sub>rr</sub>         |                                                                                                  |      | 28       | 55     | ns     |  |

| Body Diode Reverse Recovery Charge            | Q <sub>rr</sub>         | L = 10.4 dl/dt = 100.4/we T = 25.90                                                              |      | 21       | 42     | nC     |  |

| Reverse Recovery Fall Time                    | t <sub>a</sub>          | $I_F = 10 \text{ A}, \text{ dI/dt} = 100 \text{ A/}\mu\text{s}, \text{ T}_J = 25 ^\circ\text{C}$ |      | 15       |        |        |  |

| Reverse Recovery Rise Time                    | t <sub>b</sub>          |                                                                                                  |      | 13       |        | ns     |  |

Notes:

a. Pulse test; pulse width  $\leq$  300  $\mu s,$  duty cycle  $\leq$  2 %.

b. Guaranteed by design, not subject to production testing.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Vishay Siliconix

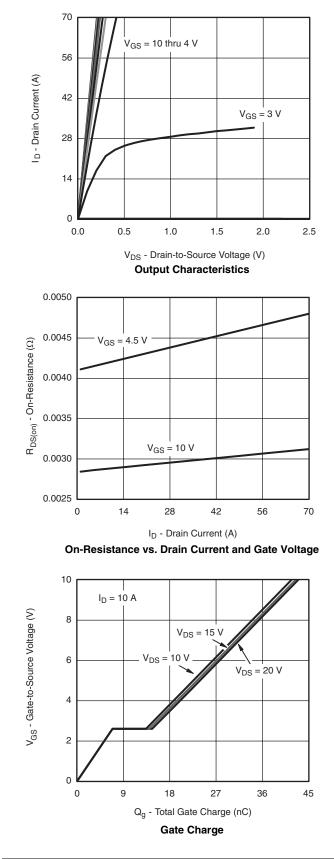

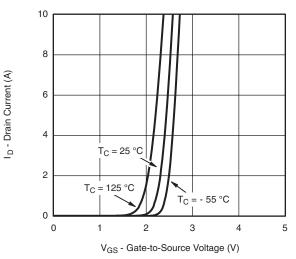

#### TYPICAL CHARACTERISTICS 25 °C, unless otherwise noted

**Transfer Characteristics**

Capacitance

Document Number: 68879 S-82018-Rev. A, 01-Sep-08

## **Vishay Siliconix**

10

10

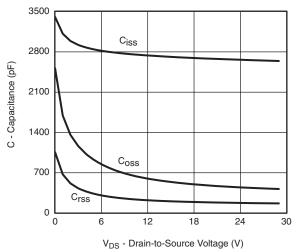

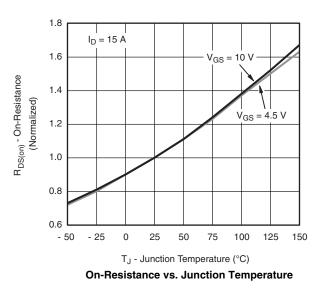

#### TYPICAL CHARACTERISTICS 25 °C, unless otherwise noted

Vishay Siliconix

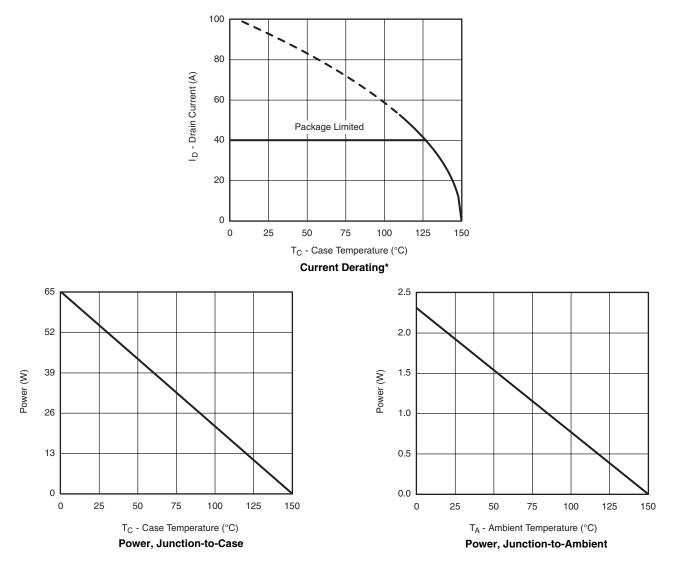

\* The power dissipation  $P_D$  is based on  $T_{J(max)} = 150$  °C, using junction-to-case thermal resistance, and is more useful in settling the upper dissipation limit for cases where additional heatsinking is used. It is used to determine the current rating, when this rating falls below the package limit.

# VISHAY.

## Vishay Siliconix

#### TYPICAL CHARACTERISTICS 25 °C, unless otherwise noted

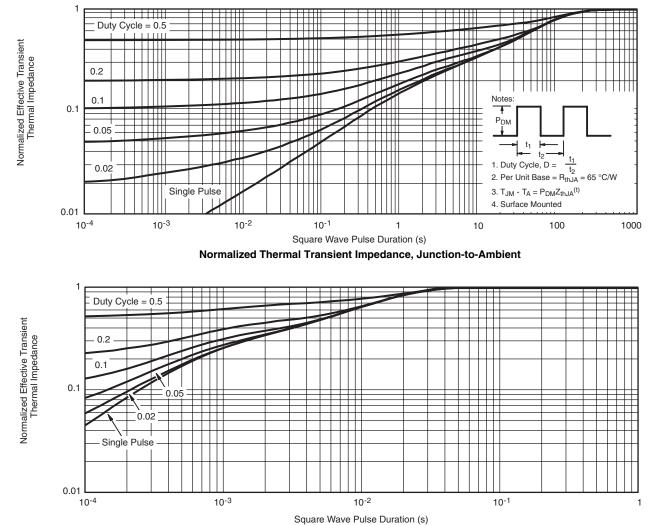

Normalized Thermal Transient Impedance, Junction-to-Case

Vishay Siliconix maintains worldwide manufacturing capability. Products may be manufactured at one of several qualified locations. Reliability data for Silicon Technology and Package Reliability represent a composite of all qualified locations. For related documents such as package/tape drawings, part marking, and reliability data, see http://www.vishay.com/ppg?68879.

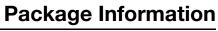

## Vishay Siliconix

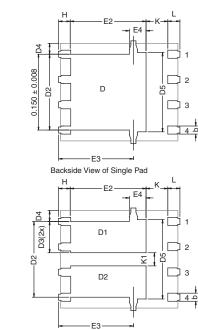

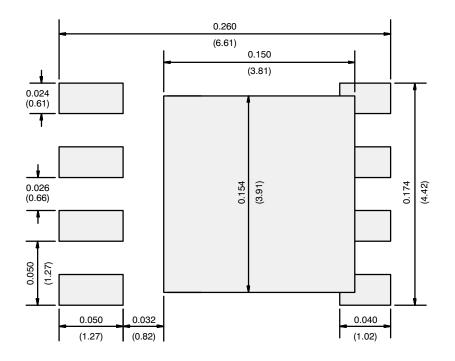

#### PowerPAK<sup>®</sup> SO-8, (SINGLE/DUAL)

#### Notes

1. Inch will govern.

2 Dimensions exclusive of mold gate burrs.

3. Dimensions exclusive of mold flash and cutting burrs.

θ

θ

Ζ

۲

A1-

Detail Z

-@54

Backside View of Dual Pad

|               |                  | MILLIMETERS           |      |             | INCHES     |       |  |

|---------------|------------------|-----------------------|------|-------------|------------|-------|--|

| DIM.          | MIN.             | NOM.                  | MAX. | MIN.        | NOM.       | MAX.  |  |

| А             | 0.97             | 1.04                  | 1.12 | 0.038       | 0.041      | 0.044 |  |

| A1            | 0.00             | -                     | 0.05 | 0.000       | -          | 0.002 |  |

| b             | 0.33             | 0.41                  | 0.51 | 0.013       | 0.016      | 0.020 |  |

| С             | 0.23             | 0.28                  | 0.33 | 0.009       | 0.011      | 0.013 |  |

| D             | 5.05             | 5.15                  | 5.26 | 0.199       | 0.203      | 0.207 |  |

| D1            | 4.80             | 4.90                  | 5.00 | 0.189       | 0.193      | 0.197 |  |

| D2            | 3.56             | 3.76                  | 3.91 | 0.140       | 0.148      | 0.154 |  |

| D3            | 1.32             | 1.50                  | 1.68 | 0.052       | 0.059      | 0.066 |  |

| D4            |                  | 0.57 TYP.             |      | 0.0225 TYP. |            |       |  |

| D5            |                  | 3.98 TYP.             |      | 0.157 TYP.  |            |       |  |

| Е             | 6.05             | 6.15                  | 6.25 | 0.238       | 0.242      | 0.246 |  |

| E1            | 5.79             | 5.89                  | 5.99 | 0.228       | 0.232      | 0.236 |  |

| E2            | 3.48             | 3.66                  | 3.84 | 0.137       | 0.144      | 0.151 |  |

| E3            | 3.68             | 3.78                  | 3.91 | 0.145       | 0.149      | 0.154 |  |

| E4            |                  | 0.75 TYP.             |      | 0.030 TYP.  |            |       |  |

| е             |                  | 1.27 BSC              |      | 0.050 BSC   |            |       |  |

| K             |                  | 1.27 TYP.             |      |             | 0.050 TYP. |       |  |

| K1            | 0.56             | -                     | -    | 0.022       | -          | -     |  |

| Н             | 0.51             | 0.61                  | 0.71 | 0.020       | 0.024      | 0.028 |  |

| L             | 0.51             | 0.61                  | 0.71 | 0.020       | 0.024      | 0.028 |  |

| L1            | 0.06             | 0.13                  | 0.20 | 0.002       | 0.005      | 0.008 |  |

| θ             | 0°               | -                     | 12°  | 0°          | -          | 12°   |  |

| W             | 0.15             | 0.25                  | 0.36 | 0.006       | 0.010      | 0.014 |  |

| М             |                  | 0.125 TYP. 0.005 TYP. |      |             |            |       |  |

| I: T10-0055-R | ev. J, 15-Feb-10 |                       |      | •           |            |       |  |

# **PowerPAK<sup>®</sup> SO-8 Mounting and Thermal Considerations**

#### Wharton McDaniel

MOSFETs for switching applications are now available with die on resistances around 1 m $\Omega$  and with the capability to handle 85 A. While these die capabilities represent a major advance over what was available just a few years ago, it is important for power MOSFET packaging technology to keep pace. It should be obvious that degradation of a high performance die by the package is undesirable. PowerPAK is a new package technology that addresses these issues. In this application note, PowerPAK's construction is described. Following this mounting information is presented including land patterns and soldering profiles for maximum reliability. Finally, thermal and electrical performance is discussed.

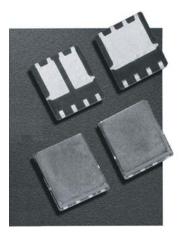

#### THE PowerPAK PACKAGE

The PowerPAK package was developed around the SO-8 package (Figure 1). The PowerPAK SO-8 utilizes the same footprint and the same pin-outs as the standard SO-8. This allows PowerPAK to be substituted directly for a standard SO-8 package. Being a leadless package, PowerPAK SO-8 utilizes the entire SO-8 footprint, freeing space normally occupied by the leads, and thus allowing it to hold a larger die than a standard SO-8. In fact, this larger die is slightly larger than a full sized DPAK die. The bottom of the die attach pad is exposed for the purpose of providing a direct, low resistance thermal path to the substrate the device is mounted on. Finally, the package height is lower than the standard SO-8, making it an excellent choice for applications with space constraints.

Figure 1. PowerPAK 1212 Devices

#### **PowerPAK SO-8 SINGLE MOUNTING**

The PowerPAK single is simple to use. The pin arrangement (drain, source, gate pins) and the pin dimensions are the same as standard SO-8 devices (see Figure 2). Therefore, the PowerPAK connection pads match directly to those of the SO-8. The only difference is the extended drain connection area. To take immediate advantage of the PowerPAK SO-8 single devices, they can be mounted to existing SO-8 land patterns.

Standard SO-8 PowerPAK SO-8

#### Figure 2.

The minimum land pattern recommended to take full advantage of the PowerPAK thermal performance see Application Note 826, <u>Recommended Minimum Pad</u> <u>Patterns With Outline Drawing Access for Vishay Siliconix MOSFETs</u>. Click on the PowerPAK SO-8 single in the index of this document.

In this figure, the drain land pattern is given to make full contact to the drain pad on the PowerPAK package.

This land pattern can be extended to the left, right, and top of the drawn pattern. This extension will serve to increase the heat dissipation by decreasing the thermal resistance from the foot of the PowerPAK to the PC board and therefore to the ambient. Note that increasing the drain land area beyond a certain point will yield little decrease in foot-to-board and foot-to-ambient thermal resistance. Under specific conditions of board configuration, copper weight and layer stack, experiments have found that more than about 0.25 to  $0.5 \text{ in}^2$  of additional copper (in addition to the drain land) will yield little improvement in thermal performance.

## Vishay Siliconix

#### PowerPAK SO-8 DUAL

The pin arrangement (drain, source, gate pins) and the pin dimensions of the PowerPAK SO-8 dual are the same as standard SO-8 dual devices. Therefore, the PowerPAK device connection pads match directly to those of the SO-8. As in the single-channel package, the only exception is the extended drain connection area. Manufacturers can likewise take immediate advantage of the PowerPAK SO-8 dual devices by mounting them to existing SO-8 dual land patterns.

To take the advantage of the dual PowerPAK SO-8's thermal performance, the minimum recommended land pattern can be found in Application Note 826, *Recommended Minimum Pad Patterns With Outline Drawing Access for Vishay Siliconix MOSFETs.* Click on the PowerPAK 1212-8 dual in the index of this document.

The gap between the two drain pads is 24 mils. This matches the spacing of the two drain pads on the PowerPAK SO-8 dual package.

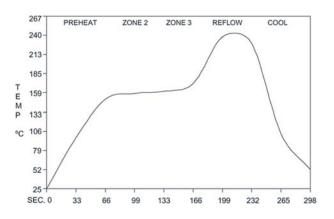

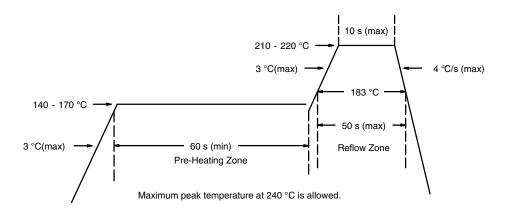

#### **REFLOW SOLDERING**

Vishay Siliconix surface-mount packages meet solder reflow reliability requirements. Devices are subjected to solder reflow as a test preconditioning and are then reliability-tested using temperature cycle, bias humidity, HAST, or pressure pot. The solder reflow temperature profile used, and the temperatures and time duration, are shown in Figures 3 and 4.

For the lead (Pb)-free solder profile, see http:// www.vishay.com/doc?73257.

| Ramp-Up Rate                | + 6 °C /Second Maximum |

|-----------------------------|------------------------|

| Temperature at 155 ± 15 °C  | 120 Seconds Maximum    |

| Temperature Above 180 °C    | 70 - 180 Seconds       |

| Maximum Temperature         | 240 + 5/- 0 °C         |

| Time at Maximum Temperature | 20 - 40 Seconds        |

| Ramp-Down Rate              | + 6 °C/Second Maximum  |

Figure 3. Solder Reflow Temperature Profile

#### THERMAL PERFORMANCE

#### Introduction

A basic measure of a device's thermal performance is the junction-to-case thermal resistance,  $R\theta_{jc}$ , or the junction-to-foot thermal resistance,  $R\theta_{jf}$ . This parameter is measured for the device mounted to an infinite heat sink and is therefore a characterization of the device only, in other words, independent of the properties of the object to which the device is mounted. Table 1 shows a comparison of the DPAK, PowerPAK SO-8, and standard SO-8. The PowerPAK has thermal performance equivalent to the DPAK, while having an order of magnitude better thermal performance over the SO-8.

| TABLE 1.                                                      |          |                  |                  |  |  |  |  |

|---------------------------------------------------------------|----------|------------------|------------------|--|--|--|--|

| DPAK and PowerPAK SO-8<br>Equivalent Steady State Performance |          |                  |                  |  |  |  |  |

|                                                               | DPAK     | PowerPAK<br>SO-8 | Standard<br>SO-8 |  |  |  |  |

| Thermal Resistance $R\theta_{jc}$                             | 1.2 °C/W | 1.0 °C/W         | 16 °C/W          |  |  |  |  |

#### Thermal Performance on Standard SO-8 Pad Pattern

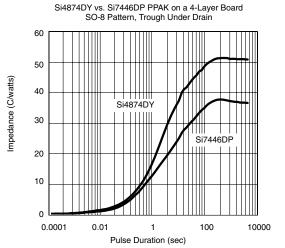

Because of the common footprint, a PowerPAK SO-8 can be mounted on an existing standard SO-8 pad pattern. The question then arises as to the thermal performance of the PowerPAK device under these conditions. A characterization was made comparing a standard SO-8 and a PowerPAK device on a board with a trough cut out underneath the PowerPAK drain pad. This configuration restricted the heat flow to the SO-8 land pads. The results are shown in Figure 5.

Because of the presence of the trough, this result suggests a minimum performance improvement of 10  $^{\circ}C/W$  by using a PowerPAK SO-8 in a standard SO-8 PC board mount.

The only concern when mounting a PowerPAK on a standard SO-8 pad pattern is that there should be no traces running between the body of the MOSFET. Where the standard SO-8 body is spaced away from the pc board, allowing traces to run underneath, the Power-PAK sits directly on the pc board.

#### **Thermal Performance - Spreading Copper**

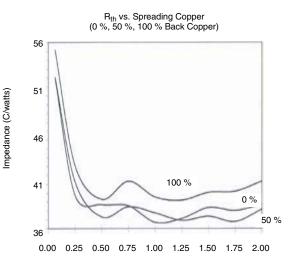

Designers may add additional copper, spreading copper, to the drain pad to aid in conducting heat from a device. It is helpful to have some information about the thermal performance for a given area of spreading copper.

Figure 6 shows the thermal resistance of a PowerPAK SO-8 device mounted on a 2-in. 2-in., four-layer FR-4 PC board. The two internal layers and the backside layer are solid copper. The internal layers were chosen as solid copper to model the large power and ground planes common in many applications. The top layer was cut back to a smaller area and at each step junction-to-ambient thermal resistance measurements were taken. The results indicate that an area above 0.3 to 0.4 square inches of spreading copper gives no additional thermal performance improvement. A subsequent experiment was run where the copper on the back-side was reduced, first to 50 % in stripes to mimic circuit traces, and then totally removed. No significant effect was observed.

Figure 6. Spreading Copper Junction-to-Ambient Performance

### Vishay Siliconix

#### SYSTEM AND ELECTRICAL IMPACT OF PowerPAK SO-8

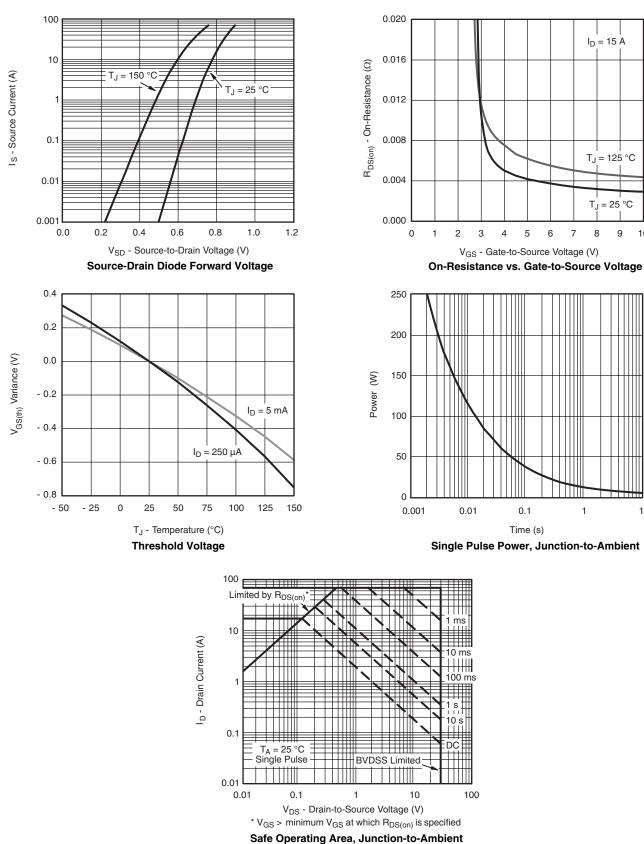

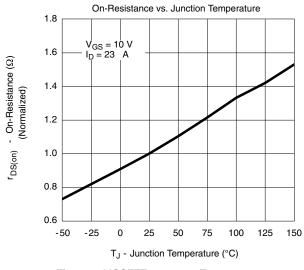

In any design, one must take into account the change in MOSFET  $r_{DS(on)}$  with temperature (Figure 7).

Figure 7. MOSFET r<sub>DS(on)</sub> vs. Temperature

A MOSFET generates internal heat due to the current passing through the channel. This self-heating raises the junction temperature of the device above that of the PC board to which it is mounted, causing increased power dissipation in the device. A major source of this problem lies in the large values of the junction-to-foot thermal resistance of the SO-8 package.

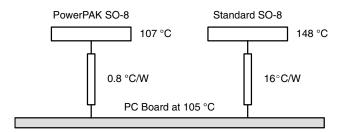

PowerPAK SO-8 minimizes the junction-to-board thermal resistance to where the MOSFET die temperature is very close to the temperature of the PC board. Consider two devices mounted on a PC board heated to 105 °C by other components on the board (Figure 8).

Figure 8. Temperature of Devices on a PC Board

Suppose each device is dissipating 2.7 W. Using the junction-to-foot thermal resistance characteristics of the PowerPAK SO-8 and the standard SO-8, the die temperature is determined to be 107 °C for the PowerPAK (and for DPAK) and 148 °C for the standard SO-8. This is a 2 °C rise above the board temperature for the PowerPAK and a 43 °C rise for the standard SO-8. Referring to Figure 7, a 2 °C difference has minimal effect on  $r_{DS(on)}$ .

Minimizing the thermal rise above the board temperature by using PowerPAK has not only eased the thermal design but it has allowed the device to run cooler, keep  $r_{DS(on)}$  low, and permits the device to handle more current than the same MOSFET die in the standard SO-8 package.

#### CONCLUSIONS

PowerPAK SO-8 has been shown to have the same thermal performance as the DPAK package while having the same footprint as the standard SO-8 package. The PowerPAK SO-8 can hold larger die approximately equal in size to the maximum that the DPAK can accommodate implying no sacrifice in performance because of package limitations.

Recommended PowerPAK SO-8 land patterns are provided to aid in PC board layout for designs using this new package.

Thermal considerations have indicated that significant advantages can be gained by using PowerPAK SO-8 devices in designs where the PC board was laid out for the standard SO-8. Applications experimental data gave thermal performance data showing minimum and typical thermal performance in a SO-8 environment, plus information on the optimum thermal performance obtainable including spreading copper. This further emphasized the DPAK equivalency.

PowerPAK SO-8 therefore has the desired small size characteristics of the SO-8 combined with the attractive thermal characteristics of the DPAK package.

# Application Note 826

Vishay Siliconix

#### RECOMMENDED MINIMUM PADS FOR PowerPAK® SO-8 Single

Recommended Minimum Pads Dimensions in Inches/(mm)

Return to Index

Vishay

## Disclaimer

ALL PRODUCT, PRODUCT SPECIFICATIONS AND DATA ARE SUBJECT TO CHANGE WITHOUT NOTICE TO IMPROVE RELIABILITY, FUNCTION OR DESIGN OR OTHERWISE.

Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively, "Vishay"), disclaim any and all liability for any errors, inaccuracies or incompleteness contained in any datasheet or in any other disclosure relating to any product.

Vishay makes no warranty, representation or guarantee regarding the suitability of the products for any particular purpose or the continuing production of any product. To the maximum extent permitted by applicable law, Vishay disclaims (i) any and all liability arising out of the application or use of any product, (ii) any and all liability, including without limitation special, consequential or incidental damages, and (iii) any and all implied warranties, including warranties of fitness for particular purpose, non-infringement and merchantability.

Statements regarding the suitability of products for certain types of applications are based on Vishay's knowledge of typical requirements that are often placed on Vishay products in generic applications. Such statements are not binding statements about the suitability of products for a particular application. It is the customer's responsibility to validate that a particular product with the properties described in the product specification is suitable for use in a particular application. Parameters provided in datasheets and/or specifications may vary in different applications and performance may vary over time. All operating parameters, including typical parameters, must be validated for each customer application by the customer's technical experts. Product specifications do not expand or otherwise modify Vishay's terms and conditions of purchase, including but not limited to the warranty expressed therein.

Except as expressly indicated in writing, Vishay products are not designed for use in medical, life-saving, or life-sustaining applications or for any other application in which the failure of the Vishay product could result in personal injury or death. Customers using or selling Vishay products not expressly indicated for use in such applications do so at their own risk. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay. Product names and markings noted herein may be trademarks of their respective owners.

# **Material Category Policy**

Vishay Intertechnology, Inc. hereby certifies that all its products that are identified as RoHS-Compliant fulfill the definitions and restrictions defined under Directive 2011/65/EU of The European Parliament and of the Council of June 8, 2011 on the restriction of the use of certain hazardous substances in electrical and electronic equipment (EEE) - recast, unless otherwise specified as non-compliant.

Please note that some Vishay documentation may still make reference to RoHS Directive 2002/95/EC. We confirm that all the products identified as being compliant to Directive 2002/95/EC conform to Directive 2011/65/EU.

Vishay Intertechnology, Inc. hereby certifies that all its products that are identified as Halogen-Free follow Halogen-Free requirements as per JEDEC JS709A standards. Please note that some Vishay documentation may still make reference to the IEC 61249-2-21 definition. We confirm that all the products identified as being compliant to IEC 61249-2-21 conform to JEDEC JS709A standards.